案例&資訊

從三個層面認(rèn)識SRAM存儲器

來源:宇芯有限公司 日期:2020-08-31 10:33:25

大家都了解,CPU是負(fù)責(zé)計算和處理的,而存儲器則是負(fù)責(zé)互換數(shù)據(jù)信息的。有些人是那么形容的,說CPU便是技術(shù)工程師自己,運行內(nèi)存就好像操作臺,必須妥善處理的物品必須先取得工作中臺子上才便捷解決。那么硬盤是什么呢?電腦硬盤如同木柜,儲放電子元器件儀器設(shè)備用的庫房,存物品。下面專注于代理銷售SRAM、MRAM、Flash等存儲芯片供應(yīng)商宇芯電子從三個層次介紹SRAM。

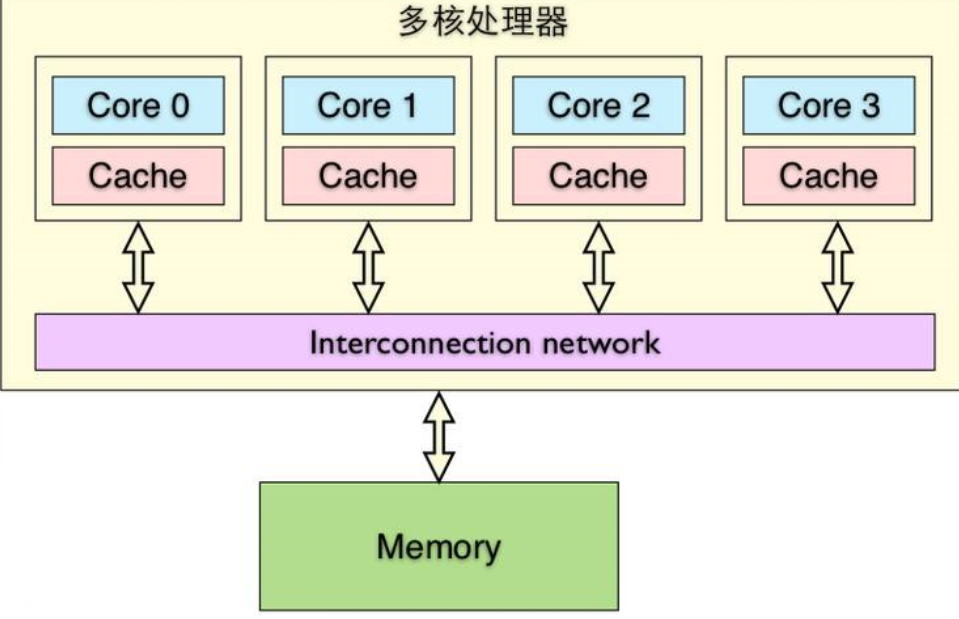

存儲器有兩個基礎(chǔ)的組成模塊,充足了解SRAM和DRAM這兩個定義及其電路原理,針對學(xué)習(xí)工具CPU架構(gòu)及其DDR十分有效。DRAM便是動態(tài)隨機存儲器,SRAM是靜態(tài)數(shù)據(jù)隨機存儲器。這一動一靜的實質(zhì)是什么呢?先說靜態(tài)數(shù)據(jù)隨機存儲器,它是運用如D觸發(fā)器的構(gòu)造來進行數(shù)據(jù)信息的載入與載入的,材料的載入不用刷新動作,那樣不用更新動作的就變成靜態(tài)數(shù)據(jù)。那樣促使控制系統(tǒng)設(shè)計非常簡單,存儲的速率比DRAM快許多。適用于于髙速儲存的應(yīng)用領(lǐng)域例如CPU的cache緩存文件。

了解完靜態(tài)數(shù)據(jù)隨機存儲器以后,動態(tài)性隨機存儲器就比較好了解。動態(tài)性是指運用電容器的蓄電池充電來完成材料的載入與載入姿勢,由于電容器會漸漸地充放電,假如充放電到閥值下列,數(shù)據(jù)信息很有可能便會遺失了,因而必須每過一段時間來做更新的姿勢,以維持材料的一致性。最普遍的便是手機上和電腦上的運行內(nèi)存了。

1、第一層了解—一個D觸發(fā)器組成非常簡單SRAM

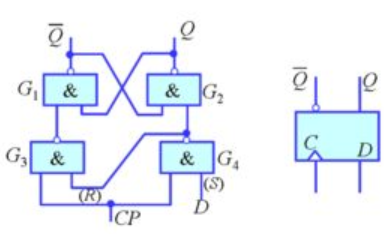

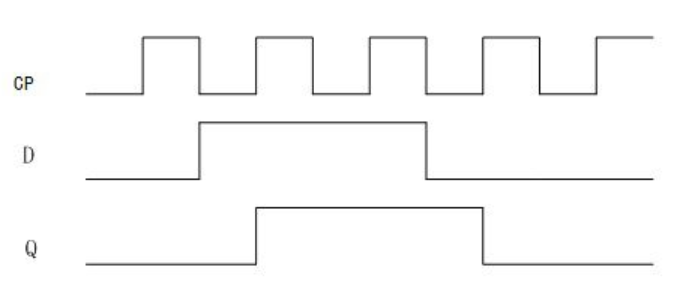

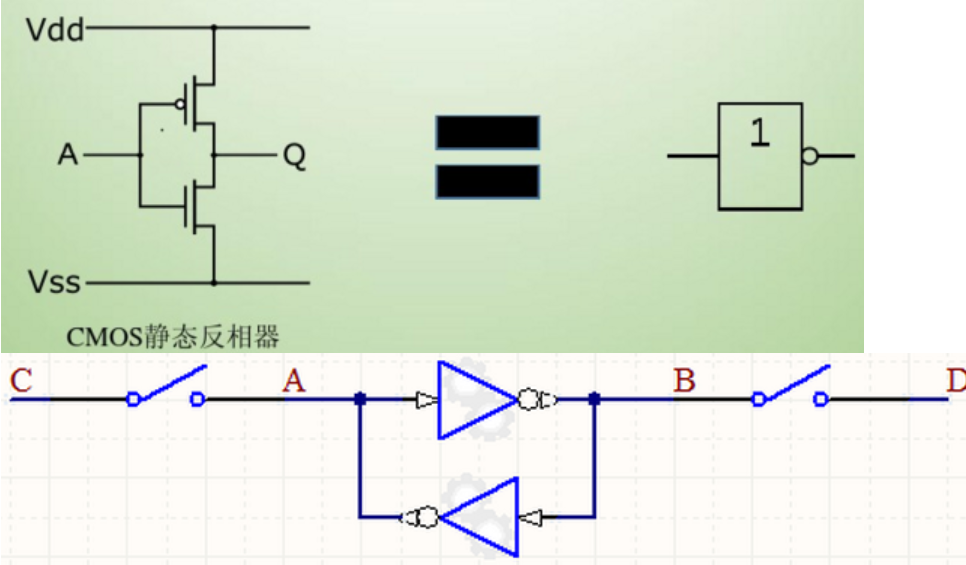

首先從最基本數(shù)字電路設(shè)計開始。有一個很基礎(chǔ)且深刻的認(rèn)識:SRAM cell最簡單的構(gòu)成單元就是一個D觸發(fā)器,如下圖所顯示的D觸發(fā)器是數(shù)字電路設(shè)計系統(tǒng)軟件里邊的一個基礎(chǔ)模塊。

1bit的SRAM模塊的關(guān)鍵電源電路便是一個D觸發(fā)器。當(dāng)有power存有的情況下,由于D觸發(fā)器的特點,數(shù)據(jù)信息能夠儲存,不用刷新。觸發(fā)器原理是具備記憶力作用的,具備2個平穩(wěn)的信息內(nèi)容存儲狀態(tài)。D觸發(fā)器的特點方程組是:Q(n+1)=D;也就是記憶力前一個情況,能夠從RS觸發(fā)器考慮,寫一下真值表,測算就很好了解了。

2、第二層了解—4個多管組成的SRAM

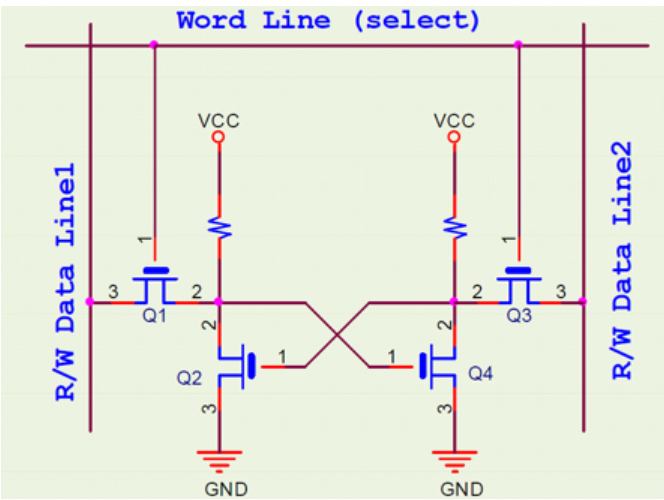

隨后,可以用基礎(chǔ)晶體三極管方面來構(gòu)建一個簡易的SRAM模塊,只是由4個NMOS管和2個電阻器組成的。

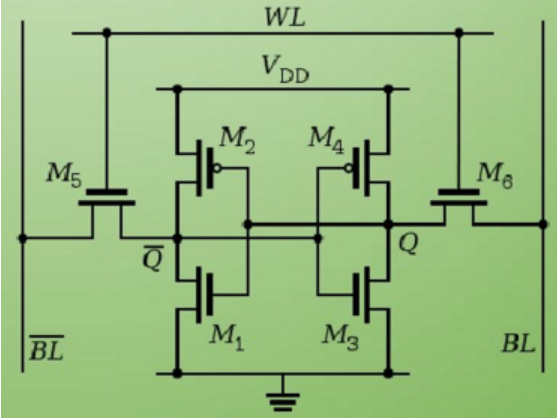

3、第三層了解--6管多管組成的SRAM

最終,能夠從IC的生產(chǎn)制造方面看來。實際上絕大多數(shù)與第二層類似,僅僅M2與M4用PMOS替代。SRAM中的每一bit儲存在由四個場效管(M1,M2,M3,M4)組成2個交叉耦合的反相器中。此外2個場效管(M5,M6)是儲存基礎(chǔ)模塊到用以讀寫能力基準(zhǔn)線(BitLine)的自動開關(guān)。

一個SRAM基礎(chǔ)模塊有0和12個脈沖信號平穩(wěn)情況。SRAM基礎(chǔ)模塊由2個CMOS反相器構(gòu)成。2個反相器的鍵入、輸出交叉式聯(lián)接,即第一個反相器的輸出聯(lián)接第二個反相器的鍵入,第二個反相器的輸出聯(lián)接第一個反相器的鍵入。這就能完成2個反相器的輸出情況的鎖住、儲存,即儲存了一個位元的情況。

關(guān)鍵詞:SRAM

宇芯有限公司自成立以來,我們專注于代理國內(nèi)外各大知名品牌的半導(dǎo)體元器件,代理品牌有NETSOL、JSC、everspin代理、來楊Lyontek、ISSI、CYPRESS,VTI等多個品牌總代理資質(zhì),主要產(chǎn)品線為sram、mram、psram等其他存儲器芯片,致力于為客戶提供具有競爭優(yōu)勢的產(chǎn)品,是一家專業(yè)提供存儲方案解決商。

相關(guān)文章:雙端口SRAM中讀干擾問題